Und weiter gehts...

Nach dem wir die wichtigste Infromation herausgefunden haben, kann man sich an der Hardware konzentrieren.

Als ich schon im Annonce erwähnt habe, dass ist schon die dritte Version des Players, also ich habe da nicht viel Neues im Bereich Hardware getan. Nur aus der zweite Version einpaar unnötige Teile herausgeschmiessen, und die Platine neu gelayoutet, um an die Göße der 2.5 Zoll Festplatte anzupassen. Die Schaltung des Player sebls kann man hier runterladen. Und hier liegt die Schaltung des Display-Modules

Gehen wird durch die wichtigste Blöcke.

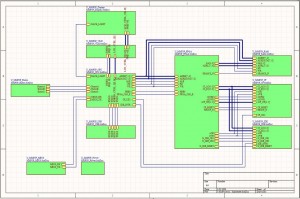

Auf der ersten Seite ist die Blockschaltung des ganzen Player dargestelt.

Wie man sieht, der Player ist eigentlich ganz einfach. Auf der Blockschaltung sind volgende Module dargestellt:

- Power — unser Netzteil

- M-Bus — Autoradio interface

- Button — Bedienungseinheit — Dreheimpulsgeber

- CPU— Hier ist allec klar — Das Gehirn useres Players — ATMega128

- VLSI — Audio — MP3 Decoder

- Display — Nokia 3310 Display

- USB — UART <-> USB <-> Serielle Converter

- FPGA — Programmierbares Logick Xilinx XC95144XL

- RAM — 512 kB SRAM von Samsung — K6X4008C1F.

- CF, IDE — Compact Flash und Festplatte 2.5 Zoll

Es kommen Fragen an, warum CF und nicht, zum Beispiel, SD/MMC Karten. Hier sind Antworten:

- Erstens, ich habe viel CF Konnetktoren gefunden. Und für CF/MMC musste ich die noch kaufen.

- Zweitens, Programmmässig, es gibd keinen Unterschied zwischen CF und IDE. Man muss nur die Zugriffsadresse beachten, alles anderes ist gleich. Für SD/MMC musste ich noch den Treiber neu schreiben.

Fangen wir von den einfachen Blöcken an:

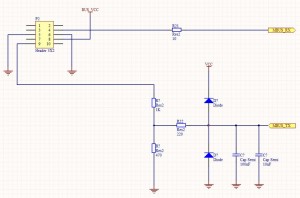

* Power — Netzteil. die Stromversorgnung bekommte der vom M-Bus Konnektor — 12 Volts. Und wandelt die in 3.3 Volts für CPLD und VLS MP3 Dekoder, und 5 Volts für alles anderes. Gebaut auf der Basis von der LM2575-T-5 Schaltung und Linealer Regler MC33275.

* Button — Normales Impulsdrehegeber mit Fasenkodierung der Dreherichtung.

* USB — der alte gute FTDI FT232BM USB-Seriel Konverter

* M-Bus — Hier wird es schon interessant. Der Datasignal ist TTL 5 Volts Signal. Über den Protokol sprechen wir in anderem Artikel. Also gibt es an ACC Signal — wenn Zündschlüssel eingesteckt und auf eine Raste gedreht. In dem Fall wird Extraanlagen (Accessories) eingeschaltet. Dieser Signal ist 12 Volts, desswegen musste ich den Spannungsteiler machen:

Mit diesen Werten werden 12 Volts in ca. 4.5 Volts konvertiert. Wenn die Spannung am Eingang plotzlich bis 16 Volts springt, dann am Ausgang werden 5.5 Volts, was für unserem Mikrokontroller noch akzeptabel ist. Dioden müssen solche Sprünge begrenzen.

Warum brauchen wir überhaupt den ACC Signal zu überwachen. Desswegen, weil es in dem Protokol selbel nichts gibt, was uns sagen kann, wann wir «schalfen» gehen müssem und nicht mehr die Musick abspeilen ( Wenn ist der Fahrer den Schlüßell rausgesteckt hat). Nur diesen Signal haben wir dafür.

*Display, VLSI — hier ist alles, wie in Datenblätter.

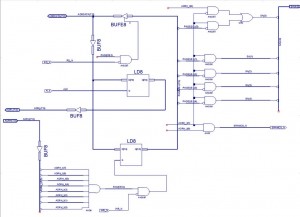

* Mit dem RAM ist auch interessant, weil das 512 kB Speicher sind. Aber laut Datenblatt von Atmel, ATMega128 kann nur 64 kB externen Speicher adressieren, dafür aber auch müssen einige Sachen gemacht werden, sonst kann er nur 60 kB sehen. Um diese Begrenzung umzugehen, brauchen wird CPLD, in dem ganze adressierungs-Prozess gemacht wird. Es werden Speicher-Banks eingfuhgt. Jede Bank ist 16384 kBytes groß. Insgesamt 32 Banks. Super!

Die Schaltung der Speicherverwaltung ist von dem EtherNut Projekt entnommen wurde. Ich bin der Meinung, dass da die Entwicklern einiges nicht ganz richtig gemacht haben, und Bank mit Nummer 0 ist gleche Bank, wie der Bank mit Nummer 31. Ich habe sehr tief in die Details nicht reingegangen, habe einfach 31. Bank aus Benutzung ausgeschloßen.

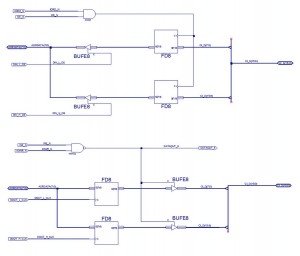

*СF/IDE — der Anschluß mach keine Problemme und da gibt es nicht viel zu sagen. Wirkliche Schwierigkeiten werden später — in der Software. Ganze Zugriffskontrol zu dem CF und Festplatte ist durch CPLD gesteuert. Für die Software sind die Festplatte und CF nur die Adresse in RAM. CF's Base-Adress ist 0xD000. Und für Festplate — 0xF000. Dass heisst, dass man in CPLD können muss, die Adresse zu verwalten. Das macht die VHDL — Datei — FPGA_IoControl_VHDL.Vhd (Alle Sourcen werden am Ende des Atikles ausefürt). Also in CPLD wird die Konvertierung von 16 Bit zu 8 Bit Datenbreite und zurück gemacht:

Es bleiben eigentlich die interessanteste Blöcke — CPLD (auf der Schaltung heisst der Block FPGA ) und CPU

* Teil des CPLD's haben wird schon angeschaut. Weitere kann man in der Sourcen anschauen. Ich sage nur, dass das Umbau von einem alterem Projekt ist, und ich habe versucht so wenig wie möglich das schon funktionierende Projekt anfassen, aber man kann da im Projekt enige unnötige Teile sehen, die man umbenennen kann, oder komplett rausschmeisen. Aber Sie wissen ja. Fass ja nicht an das funktionierende Software!

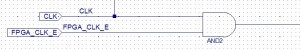

Also ins CPLD kommt CLK Signal ein, der von Oscillator, der mit 32 MHz getrieben wird. Und in CPLD selber habe ich einen Element AND2 eingebaut, um den weiteren Durchgang des Signales zu verhindern. Das hat mir... nicht viel gebracht, als ich rewartet habe — nur 1 mA Stromersparniss.

Die Ausgänge des CPLD's habe ich so platziert, dass es den Layouting Prozess erleichtert, und bringen weniger Durchkontaktierungen auf der Platine.

* Und CPU Block ist geblieben. Da gibt es aber nicht viel interessantes. Viele Leitungen und Kondesatoren. Das interessanteste in innen drin, in der Software. Darüber srechen wir aber in der nächsten Folge.

Und hier ist die Lister der Datein, die in der Artikel vorgeführt wurde

- Die Player-Schaltung -mmp3p_schematic.pdf

- Die LCD Module-Schaltung -mmp3p_schematic.pdf

- Das Projekt der Firmware für CPLD. Man benötigt WEB ISE von Xilinx dafür — mmp3p_xilinx.rar

- Datenblatt für Nokia 3310 Display Kontroller -phillips_48x84_lcd_driver.pdf

- Datenblatt für MP3 Dekoder von VLSI VS1001K -vs1001.pdf

- Datenblat für RAM Baustein von Samsung K6X4008C1F — k6x4008c1f.pdf

AVR Deices – конструкции на микроконтроллерах AVR и не только…

AVR Deices – конструкции на микроконтроллерах AVR и не только…

Оставить комментарий или два

Пожалуйста, зарегистрируйтесь для комментирования.