[lang_ru]Продолжаем разговор...[/lang_ru]

[lang_de]Und weiter gehts... [/lang_de]

[lang_ru]После того, как мы разузнали всю основную информацию, можно приступать к проектированию железа.[/lang_ru]

[lang_de]Nach dem wir die wichtigste Infromation herausgefunden haben, kann man sich an der Hardware konzentrieren.[/lang_de]

[lang_ru]Как я уже говорил в анонсе , это у меня уже третья версия, так что с железом я долго не возился. Только из второй версии выкинул ненужные детали, и развел платку под размер 2.5 дюймового диска от ноутбука. Схему самого плеера можно глянуть тут. А тут схемка блока с дисплеем. [/lang_ru]

[lang_de]Als ich schon im Annonce erwähnt habe, dass ist schon die dritte Version des Players, also ich habe da nicht viel Neues im Bereich Hardware getan. Nur aus der zweite Version einpaar unnötige Teile herausgeschmiessen, und die Platine neu gelayoutet, um an die Göße der 2.5 Zoll Festplatte anzupassen. Die Schaltung des Player sebls kann man hier runterladen. Und hier liegt die Schaltung des Display-Modules [/lang_de]

[lang_ru]Пройдемся по основным узлам.[/lang_ru]

[lang_de]Gehen wird durch die wichtigste Blöcke. [/lang_de]

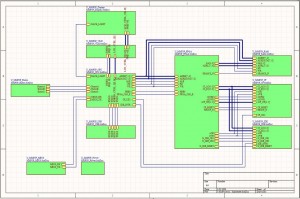

[lang_ru]На первой странице представлена «блок схема» всего плеера:[/lang_ru]

[lang_de]Auf der ersten Seite ist die Blockschaltung des ganzen Player dargestelt. [/lang_de]

[lang_ru]Как видно — плеер получился довольно простенький. На блок схеме представлены следующие модули:[/lang_ru]

[lang_de]Wie man sieht, der Player ist eigentlich ganz einfach. Auf der Blockschaltung sind volgende Module dargestellt: [/lang_de]

- [lang_ru]Power — блок питания[/lang_ru]

- [lang_de]Power — unser Netzteil[/lang_de]

- [lang_ru]M-Bus — интерфейс покдлючения к магнитоле[/lang_ru]

- [lang_de]M-Bus — Autoradio interface[/lang_de]

- [lang_ru]Button — колесо прокрутки / кнопка (Dreheimpulsgeber)[/lang_ru]

- [lang_de]Button — Bedienungseinheit — Dreheimpulsgeber[/lang_de]

- [lang_ru]CPU — ну тут все понятно — мозг и координатор всей деятельности ATMega128[/lang_ru]

- [lang_de]CPU— Hier ist allec klar — Das Gehirn useres Players — ATMega128[/lang_de]

- [lang_ru]VLSI — аудио — MP3 декодер[/lang_ru]

- [lang_de]VLSI — Audio — MP3 Decoder[/lang_de]

- [lang_ru]Display — дисплей от Nokia 3310[/lang_ru]

- [lang_de]Display — Nokia 3310 Display[/lang_de]

- [lang_ru]USB — UART <-> USB <-> Serial — конвертер[/lang_ru]

- [lang_de]USB — UART <-> USB <-> Serielle Converter[/lang_de]

- [lang_ru]FPGA — программируемая логика Xilinx XC95144XL[/lang_ru]

- [lang_de]FPGA — Programmierbares Logick Xilinx XC95144XL[/lang_de]

- [lang_ru]RAM — 512 кБ SRAM от Samsung — K6X4008C1F. [/lang_ru]

- [lang_de]RAM — 512 kB SRAM von Samsung — K6X4008C1F. [/lang_de]

- [lang_ru]CF, IDE — Compact Flash и жесткий диск 2.5 дюйма[/lang_ru]

- [lang_de]CF, IDE — Compact Flash und Festplatte 2.5 Zoll[/lang_de]

[lang_ru]Многие спрашивают — почему CF а не SD или MMC. Отвечу:[/lang_ru]

[lang_de]Es kommen Fragen an, warum CF und nicht, zum Beispiel, SD/MMC Karten. Hier sind Antworten: [/lang_de]

- [lang_ru]во первых — у меня много халявных коннекторов именно для CF, а для SD/MMC их еще покупать надо.[/lang_ru]

- [lang_de]Erstens, ich habe viel CF Konnetktoren gefunden. Und für CF/MMC musste ich die noch kaufen.[/lang_de]

- [lang_ru]во вторых — в плане программы, что CF что IDE, ничем не отличаются. Только адресом доступа (об этом позже), а для SD/MMC пришлось бы отдельный драйвер сочинять.[/lang_ru]

- [lang_de]Zweitens, Programmmässig, es gibd keinen Unterschied zwischen CF und IDE. Man muss nur die Zugriffsadresse beachten, alles anderes ist gleich. Für SD/MMC musste ich noch den Treiber neu schreiben.[/lang_de]

[lang_ru]Начнем с простеньких блоков:[/lang_ru]

[lang_de]Fangen wir von den einfachen Blöcken an: [/lang_de]

[lang_ru]* Power — блок питания. Питается от M-Bus коннектора, с которого мы получаем 12 вольт, и выдает 3.3 вольта для CPLD и VLSI MP3 декодера, и 5 вольт для всего остального. Построен на базе микросхемы LM2575 T-5 и линейного регулятора MC33275.[/lang_ru]

[lang_de] * Power — Netzteil. die Stromversorgnung bekommte der vom M-Bus Konnektor — 12 Volts. Und wandelt die in 3.3 Volts für CPLD und VLS MP3 Dekoder, und 5 Volts für alles anderes. Gebaut auf der Basis von der LM2575-T-5 Schaltung und Linealer Regler MC33275. [/lang_de]

[lang_ru]* Button — Обычный переключатель с фазовой кодировкой направления вращения и кнопкой.[/lang_ru]

[lang_de]* Button — Normales Impulsdrehegeber mit Fasenkodierung der Dreherichtung. [/lang_de]

[lang_ru]*USB — Старый, добрый FTDI FT232BM USB-Serial конвертер.[/lang_ru]

[lang_de]* USB — der alte gute FTDI FT232BM USB-Seriel Konverter [/lang_de]

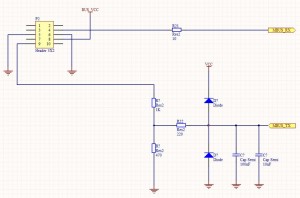

[lang_ru]*M-Bus — Тут уже интереснее. Сама линия данных — TTL 5 вольтовый сигнал. О самом протоколе будет отдельная статейка, я думаю. Так же есть сигнал ACC — когда ключ зажигания вставлен и повернут на одно деление. Тогда включается дополнительное оборудование. Этот сигнал — 12-ти вольтовый, поэтому пришлось поставить делитель:[/lang_ru]

[lang_de]* M-Bus — Hier wird es schon interessant. Der Datasignal ist TTL 5 Volts Signal. Über den Protokol sprechen wir in anderem Artikel. Also gibt es an ACC Signal — wenn Zündschlüssel eingesteckt und auf eine Raste gedreht. In dem Fall wird Extraanlagen (Accessories) eingeschaltet. Dieser Signal ist 12 Volts, desswegen musste ich den Spannungsteiler machen: [/lang_de]

[lang_ru]При этих параметрах сигнал из 12-ти вольт будет преобразован в сигнал в примерно 4.5 вольт. Если напряжение на входе скакнет до 16 вольт, то на выходе будут уже 5.5 вольт, что для микроконтроллера еще терпимо. Диоды, по идее, должны ограничивать такие скачки.[/lang_ru]

[lang_de]Mit diesen Werten werden 12 Volts in ca. 4.5 Volts konvertiert. Wenn die Spannung am Eingang plotzlich bis 16 Volts springt, dann am Ausgang werden 5.5 Volts, was für unserem Mikrokontroller noch akzeptabel ist. Dioden müssen solche Sprünge begrenzen.[/lang_de]

[lang_ru]Зачем нужно смотреть нам на этот ACC сигнал? А за тем, что бы знать, когда не играть, а идти спать. Поскольку при вытаскивании ключа с включенной магнитолой на шине не происходит ничего особенного, что бы дало нам понять, что спать пора. Этот сигнал — единственное средство, что у нас есть, что бы отловить этот момент. [/lang_ru]

[lang_de]Warum brauchen wir überhaupt den ACC Signal zu überwachen. Desswegen, weil es in dem Protokol selbel nichts gibt, was uns sagen kann, wann wir «schalfen» gehen müssem und nicht mehr die Musick abspeilen ( Wenn ist der Fahrer den Schlüßell rausgesteckt hat). Nur diesen Signal haben wir dafür.[/lang_de]

[lang_ru]*Display, VLSI — там все по даташитам.[/lang_ru]

[lang_de]*Display, VLSI — hier ist alles, wie in Datenblätter. [/lang_de]

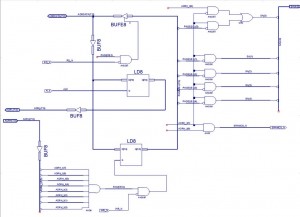

[lang_ru]*С RAM'ом тоже интересно, потому как это аж 512 кБ памяти. Но по даташиту, ATMega 128 может переварить только 64 кб внешней памяти, да и то с определенными танцами с бубном, а так — всего 60 кб. Для этого у нас есть СPLD, в которой и происходит весь процесс селектирования памяти по банкам. Один банк — 16384 байт. Всего 32 банка. Классно! [/lang_ru]

[lang_de]* Mit dem RAM ist auch interessant, weil das 512 kB Speicher sind. Aber laut Datenblatt von Atmel, ATMega128 kann nur 64 kB externen Speicher adressieren, dafür aber auch müssen einige Sachen gemacht werden, sonst kann er nur 60 kB sehen. Um diese Begrenzung umzugehen, brauchen wird CPLD, in dem ganze adressierungs-Prozess gemacht wird. Es werden Speicher-Banks eingfuhgt. Jede Bank ist 16384 kBytes groß. Insgesamt 32 Banks. Super![/lang_de]

[lang_ru]Схема управления банками памяти взята из проекта EtherNut. Но как-то мне кажется, что они там намутили немного, и теперь банк с номером 0 и банк с номером 31 являются одним и тем же банком. Я пока особо не разбирался с этим, просто исключил 31-й банк из списка используемых.[/lang_ru]

[lang_de]Die Schaltung der Speicherverwaltung ist von dem EtherNut Projekt entnommen wurde. Ich bin der Meinung, dass da die Entwicklern einiges nicht ganz richtig gemacht haben, und Bank mit Nummer 0 ist gleche Bank, wie der Bank mit Nummer 31. Ich habe sehr tief in die Details nicht reingegangen, habe einfach 31. Bank aus Benutzung ausgeschloßen. [/lang_de]

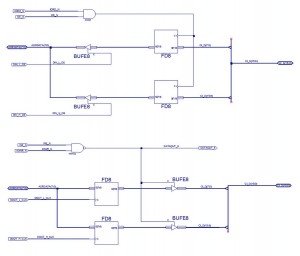

[lang_ru]*СF/IDE — Само подключение не вызывает особых вопросов. Вся сложность будет потом — в софте. Весь процесс доступа к карточке и к диску контролируется в CPLD'е. Для программы диск и карточка — это ни что иное, как адрес в памяти. CF находится по базовому адресу 0xD000, а жесткий диск — 0xF000. Значит, нам надо в CPLD уметь различать адреса. Это делает один файлик на VHDL'е — FPGA_IoControl_VHDL.Vhd (все исходники будут в конце статьи). Так же в CPLD'е просиходит процесс разбиения 16-ти битных данных в 8-ми битные при чтении и, наоборот, при записи 8-ми битных в 16-ти битные.[/lang_ru]

[lang_de]*СF/IDE — der Anschluß mach keine Problemme und da gibt es nicht viel zu sagen. Wirkliche Schwierigkeiten werden später — in der Software. Ganze Zugriffskontrol zu dem CF und Festplatte ist durch CPLD gesteuert. Für die Software sind die Festplatte und CF nur die Adresse in RAM. CF's Base-Adress ist 0xD000. Und für Festplate — 0xF000. Dass heisst, dass man in CPLD können muss, die Adresse zu verwalten. Das macht die VHDL — Datei — FPGA_IoControl_VHDL.Vhd (Alle Sourcen werden am Ende des Atikles ausefürt). Also in CPLD wird die Konvertierung von 16 Bit zu 8 Bit Datenbreite und zurück gemacht:[/lang_de]

[lang_ru]Остались самые интересные блоки — CPLD (на схеме он FPGA называется) и CPU.[/lang_ru]

[lang_de]Es bleiben eigentlich die interessanteste Blöcke — CPLD (auf der Schaltung heisst der Block FPGA ) und CPU [/lang_de]

[lang_ru]* Часть CPLD мы уже рассмотрели выше. А остальное можно поглядеть в исходниках. Скажу лишь только, что это опять же переделка готового проекта, и я старался как можно меньше менять в работающем проекте, поэтому там можно встретить некоторые ошметки от старого проекта — например, в старом проекте была статус-машина для доступа к WLAN-Карточке и организации задержек — тут же, я статус-машину убрал и просто выставляю сигналы без каких либо задержек, ну и т.д. [/lang_ru]

[lang_de] * Teil des CPLD's haben wird schon angeschaut. Weitere kann man in der Sourcen anschauen. Ich sage nur, dass das Umbau von einem alterem Projekt ist, und ich habe versucht so wenig wie möglich das schon funktionierende Projekt anfassen, aber man kann da im Projekt enige unnötige Teile sehen, die man umbenennen kann, oder komplett rausschmeisen. Aber Sie wissen ja. Fass ja nicht an das funktionierende Software! [/lang_de]

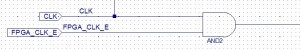

[lang_ru]Так же в CPLD входит сигнал Clock от осциллятора на 32 MHz. И в самой CPLD я поставил элемент AND2, чтобы отключить прохождение CLK по всей CPLD, когда все спят. Это дает... не очень много, как ожидалось, всего около 1мА.[/lang_ru]

[lang_de]Also ins CPLD kommt CLK Signal ein, der von Oscillator, der mit 32 MHz getrieben wird. Und in CPLD selber habe ich einen Element AND2 eingebaut, um den weiteren Durchgang des Signales zu verhindern. Das hat mir... nicht viel gebracht, als ich rewartet habe — nur 1 mA Stromersparniss. [/lang_de]

[lang_ru]Выводы CPLD я расположил таким образом, что бы при разводке платы не надо было делать переходов с одного слоя на другой, чтобы все было красивенько и, по возможности, на одном слое.[/lang_ru]

[lang_de] Die Ausgänge des CPLD's habe ich so platziert, dass es den Layouting Prozess erleichtert, und bringen weniger Durchkontaktierungen auf der Platine. [/lang_de]

[lang_ru]* Ну и CPU. На схеме ничего примечательного нету, куча проводов, да кондериков. Самое интересное в нутри, т.е. в софте. А об этом будет следующая статья.[/lang_ru]

[lang_de]* Und CPU Block ist geblieben. Da gibt es aber nicht viel interessantes. Viele Leitungen und Kondesatoren. Das interessanteste in innen drin, in der Software. Darüber srechen wir aber in der nächsten Folge. [/lang_de]

[lang_ru]А пока список файлов, использованных в этой статье:[/lang_ru]

[lang_de]Und hier ist die Lister der Datein, die in der Artikel vorgeführt wurde [/lang_de]

- [lang_ru]Схема плеера — mmp3p_schematic.pdf[/lang_ru]

- [lang_de]Die Player-Schaltung -mmp3p_schematic.pdf [/lang_de]

- [lang_ru]Схема модуля дисплея — mmp3p_lcd_shematic.pdf[/lang_ru]

- [lang_de]Die LCD Module-Schaltung -mmp3p_schematic.pdf [/lang_de]

- [lang_ru]Проект прошивки CPLD для WEB ISE от Xilinx — mmp3p_xilinx.rar[/lang_ru]

- [lang_de]Das Projekt der Firmware für CPLD. Man benötigt WEB ISE von Xilinx dafür — mmp3p_xilinx.rar [/lang_de]

- [lang_ru]Дисплей Nokia 3310 — phillips_48x84_lcd_driver.pdf[/lang_ru]

- [lang_de]Datenblatt für Nokia 3310 Display Kontroller -phillips_48x84_lcd_driver.pdf [/lang_de]

- [lang_ru]MP3 декодер VLSI VS1001K - vs1001.pdf[/lang_ru]

- [lang_de]Datenblatt für MP3 Dekoder von VLSI VS1001K -vs1001.pdf [/lang_de]

- [lang_ru]SRAM — Samsung K6X4008C1F - k6x4008c1f.pdf[/lang_ru]

- [lang_de]Datenblat für RAM Baustein von Samsung K6X4008C1F — k6x4008c1f.pdf [/lang_de]

AVR Deices – конструкции на микроконтроллерах AVR и не только…

AVR Deices – конструкции на микроконтроллерах AVR и не только…

Leave a Reply

You must be logged in to post a comment.